Époxy ep112 utilisé dans la fabrication de microélectronics

Cet article sponsorisé vous est présenté par Lien de maître.

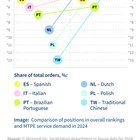

Master Bond EP112 est un système époxy thermique à deux composantes ultra-faible et isolant et isolant à deux composants conçu pour les applications exigeantes nécessitant une clarté optique et une résistance aux produits chimiques couramment utilisés dans le traitement du silicium. Cet article présente une étude de cas en deux parties impliquant une fabrication de microélectronique, présentant le rôle d’Ep112 dans la liaison d’une tranche de silicium à un substrat en verre.

Partie 1: Le processus de début et le rôle de l’EP112

Dans la première partie de cette étude de cas, les chercheurs du Lawrence Livermore National Laboratory (LLNL) ont développé un processus innovant en silicium sur isolant (SOI) appelé Start (transfert de silicium vers un substrat arbitraire). Cette méthode permet la transformation des plaquettes de silicium en vrac standard avec des circuits terminés en configurations de type SOI sans augmenter de manière significative les coûts de fabrication. En utilisant des techniques de fabrication conventionnelles, le processus de démarrage combine les avantages de l’électronique de silicium en vrac avec ceux de la technologie SOI tout en maintenant la rentabilité.

Une étape critique dans ce processus consistait à lier une tranche de silicium à un substrat de support en verre. EP112 a été sélectionné comme adhésif de choix en raison de sa viscosité ultra-bas, de fortes capacités de liaison et de sa forte résistance chimique. La structure liée a finalement contribué au développement réussi d’un prototype d’affichage des cristaux liquides (LCD), démontrant l’efficacité de l’EP112 dans la fabrication de microélectronique.

Partie 2: CMOS Éclairage de la plaquette pour la résistance aux SEU

Dans la deuxième partie de cette étude, les chercheurs de LLNL ont appliqué EP112 dans un nouveau processus d’amincissement de la plaquette pour améliorer la fiabilité des circuits intégrés basés sur les CMO (ICS). L’objectif était de réduire la sensibilité aux bouleversements d’événements (SEU) en diminuant considérablement le volume de collecte de charges dans le substrat de silicium.

Pour y parvenir, Ep112 a été utilisé pour lier deux substrats ensemble, garantissant une attachement sécurisé tout au long des étapes d’amincissement de la tranche. Le processus impliquait une étape de gravure alcaline à haute température, où la résistance chimique supérieure d’Ep112 a joué un rôle crucial dans la prévention de la déshabitation. En maintenant l’intégrité structurelle dans ces conditions difficiles, EP112 a permis de terminer le processus d’amincissement, démontrant en outre sa pertinence pour les applications avancées de semi-conducteur.

Pour en savoir plus sur les paramètres et les exigences clés et en savoir plus sur les résultats, veuillez Téléchargez l’étude de cas complète ici.